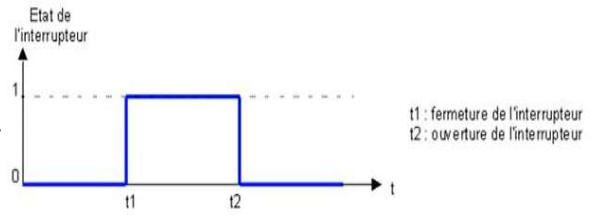

Signal logique (TOR)

Un signal est dit logique ou Tout Ou Rien (TOR) si la grandeur de l'information ne peut prendre que deux valeurs, comme :

- Vrai ou faux

- 0 ou 1

- Tension état bas ou tension état haut

- Présence ou absence

Exemples du monde réel :

- Un contact électrique peut être ouvert ou fermé

- Un signal électrique peut être présent ou absent

- Un flux infrarouge peut être réfléchi ou coupé par un obstacle

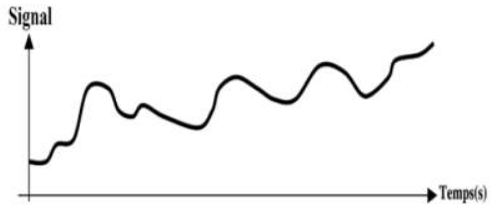

Signal analogique

Un signal est dit analogique si l'information peut prendre une infinité de valeurs de façon continue au cours du temps.

La tension est exprimée de façon continue en fonction du temps.

Exemples :

- Le signal en sortie d'un microphone

- Capteur délivrant une tension analogique

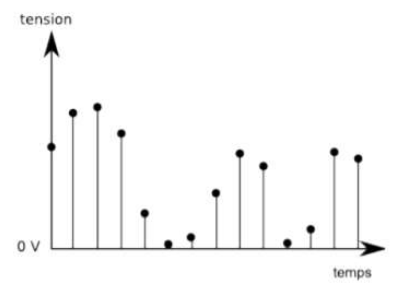

Signal numérique

Un signal est dit numérique si l'information est représentée par des valeurs non continues.

La tension est exprimée de façon discrète (discontinue) en fonction du temps.

Exemples :

- Transmission de données dans un ordinateur

- Baromètre numérique

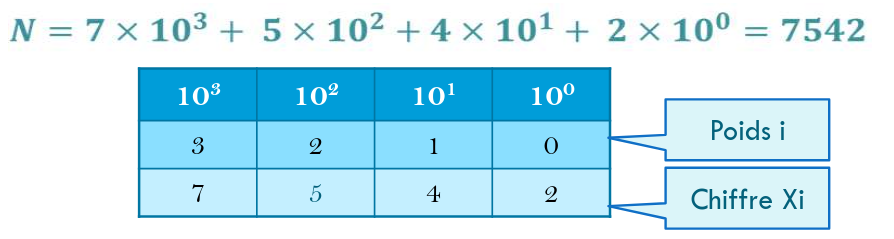

La base décimale (10)

La base 10 contient 10 chiffres, allant de 0 à 9.

MSB & LSB

Le Most Significant Bit (MSB) signifie le bit de poids fort, c'est-à-dire le bit qui se trouve le plus à gauche.

Le Least Significant Bit (LSB) signifie le bit de poids faible b0, c'est-à-dire le bit qui se trouve le plus à droite.

La base B quelconque

Soit la base B qui contient des chiffres allant de 0 à B−1.

Soit le nombre A = (XN−1 … X2 X1 X0)B contenant N chiffres.

Chaque chiffre Xi est multiplié par la base élevée à la puissance de sa position i, la somme de tous ces produits donne la valeur du nombre.

La base binaire (2)

La base binaire contient 2 chiffres : 0 et 1.

Exemple de conversion binaire → décimal :

d = (1 × 27) + (0 × 26) + (0 × 25) + (0 × 24) + (1 × 23) + (0 × 22) + (1 × 21) + (0 × 20)

d = 27 + 23 + 21

d = 128 + 8 + 2 = (138)10

La base hexadécimale (16)

La base hexadécimale contient 16 chiffres, allant de 0 à 9 puis de A à F.

| Décimal | 0 | 1 | 2 | … | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|---|---|---|---|---|---|---|---|---|---|---|---|

| Hexa | 0 | 1 | 2 | … | 9 | A | B | C | D | E | F |

Exemple de conversion hexa → décimal :

d = (8 × 161) + (A × 160)

d = (8 × 16) + (10 × 1)

d = 128 + 10 = (138)10

Cette base est née d'une lassitude des programmeurs à écrire de longues suites de 0 et de 1 (source d'erreur). Elle offre une conversion aisée de l'hexadécimale vers le binaire et vice-versa.

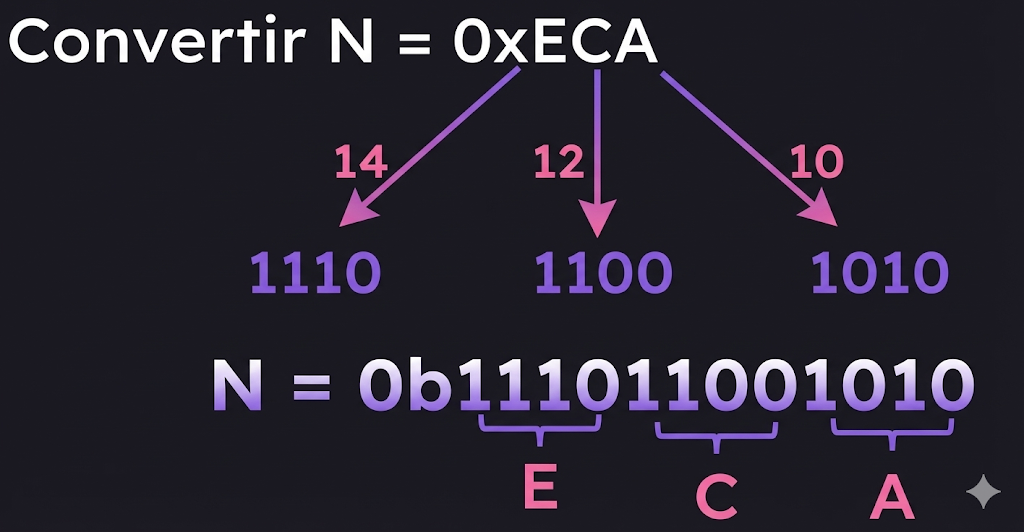

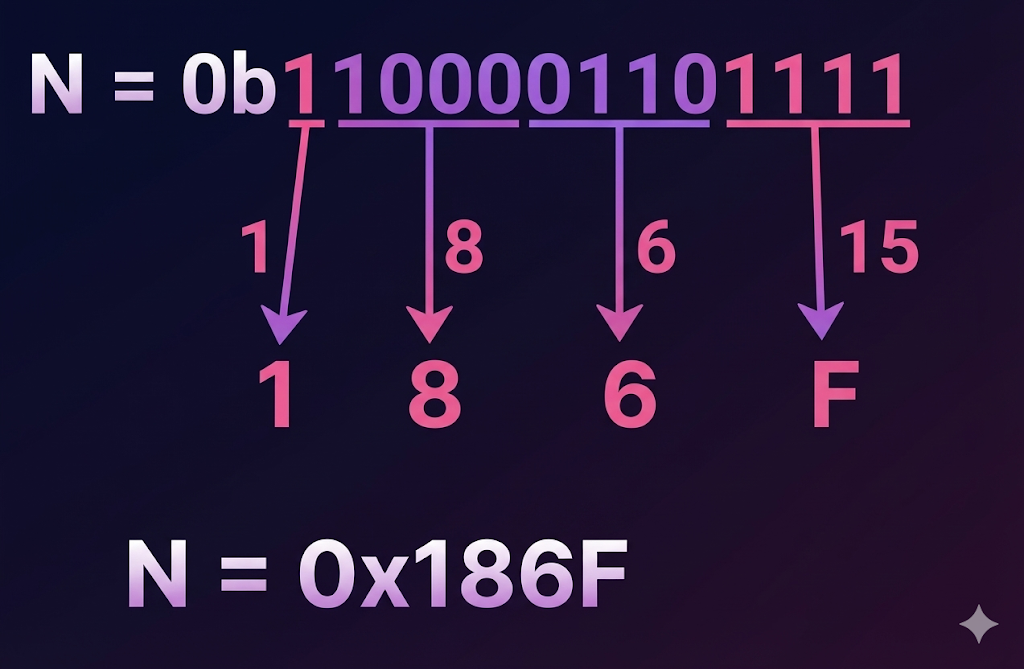

Conversion binaire ↔ hexadécimale

La conversion entre binaire et hexadécimal se fait par groupes de 4 bits (un chiffre hexadécimal = 4 bits).

Hexadécimal → Binaire

Binaire → Hexadécimal

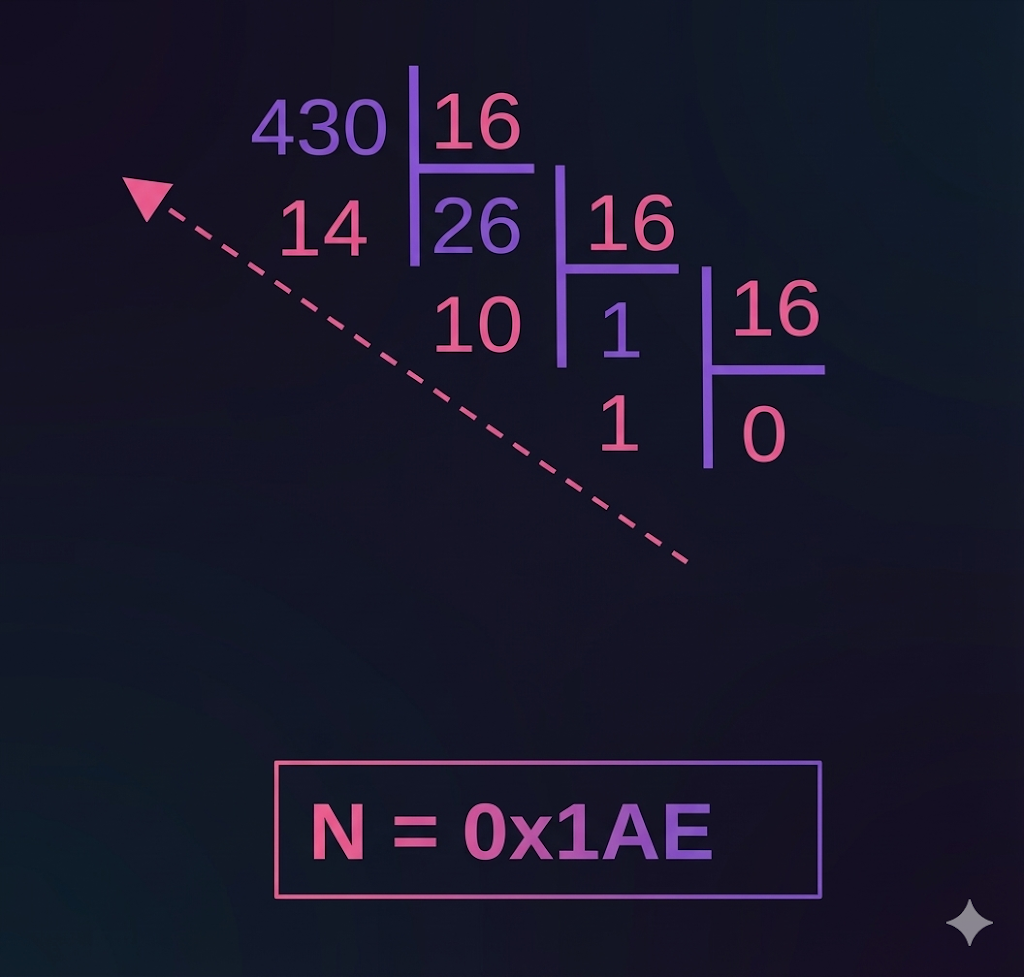

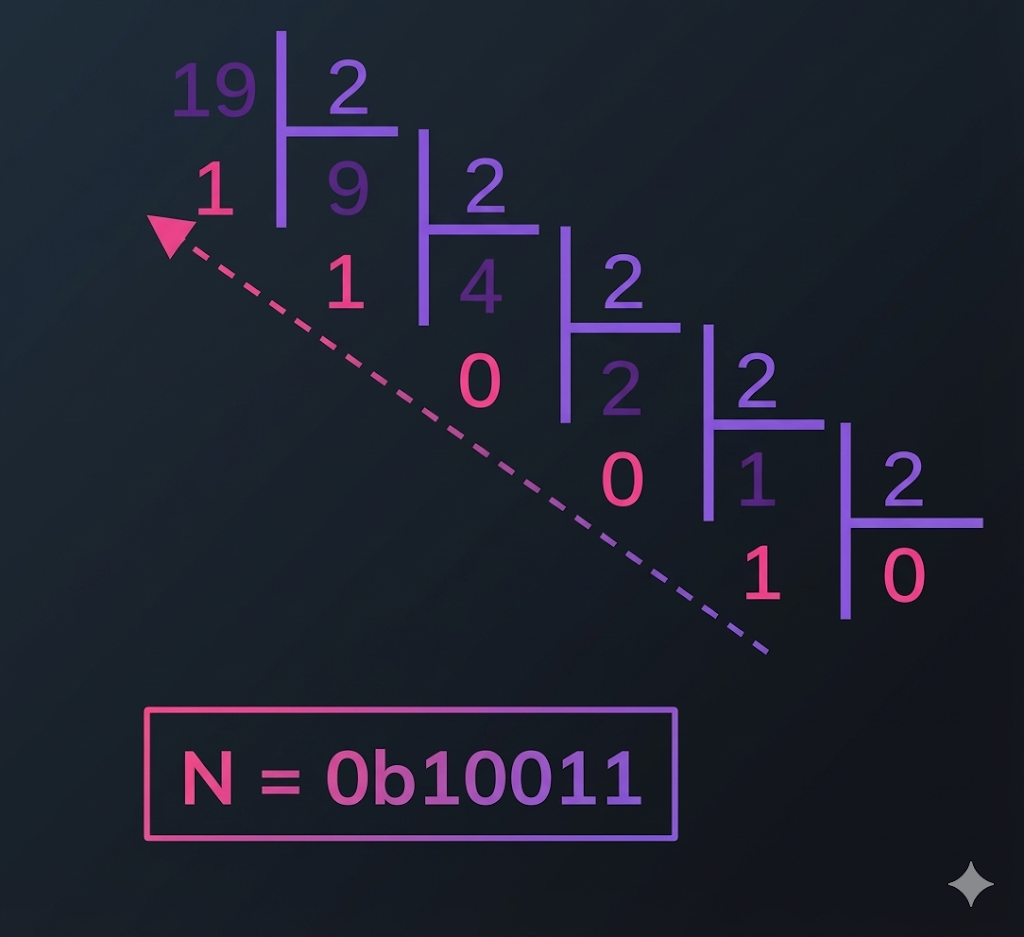

Conversion décimale → quelconque

Pour convertir un nombre décimal vers une autre base, on utilise la méthode des divisions successives par la base cible, en lisant les restes de bas en haut.

Décimal → Hexadécimal

Décimal → Binaire

Entiers naturels (non signés)

Représentation d'un nombre entier naturel S sur n bits :

Avec :

- Sn−1 : bit de poids fort (MSB)

- S0 : bit de poids faible (LSB)

Sur n bits, on peut représenter les entiers naturels de 0 à 2n−1.

Numérotation appliquée au processeur

L'addition de deux nombres entiers naturels peut engendrer un résultat supérieur à n bits : c'est l'apparition du bit de retenue Rn (retenue de l'addition des bits de rang n−1).

On dit que le résultat de cette addition n'est pas représentable sur n bits — il y a donc dépassement de capacité. Ce bit est appelé retenue ou carry (en anglais).

Dans un processeur, c'est le bit C du registre d'état qui est mis à jour par une opération d'addition générant un dépassement.

Entiers relatifs (signés)

Représentation d'un nombre entier relatif S sur n bits :

Avec :

- Sn−1 : le bit de signe

- 0 → signe positif

- 1 → signe négatif

- Sn−2 : le MSB (bit de poids fort des données)

- S0 : le LSB (bit de poids faible)

Un nombre relatif est représenté par le complément à 2 de sa valeur absolue.

Dans le cas de données codées sur 8 bits (1 octet) :

- La plus grande valeur est :

0b01111111= +127 - La plus petite valeur est :

0b10000000= −128

Extension de bit de signe

On peut représenter un nombre de taille n bits sur m bits (m > n) par extension de signe sur (m − n) bits :

- Nombre positif (bit de signe = 0) :

0101codé sur 4 bits0000 0101codé sur 8 bits (on complète avec des 0)

- Nombre négatif (bit de signe = 1) :

1001codé sur 4 bits1111 1001codé sur 8 bits (on complète avec des 1)

La règle : les bits ajoutés à gauche prennent la même valeur que le bit de signe d'origine.

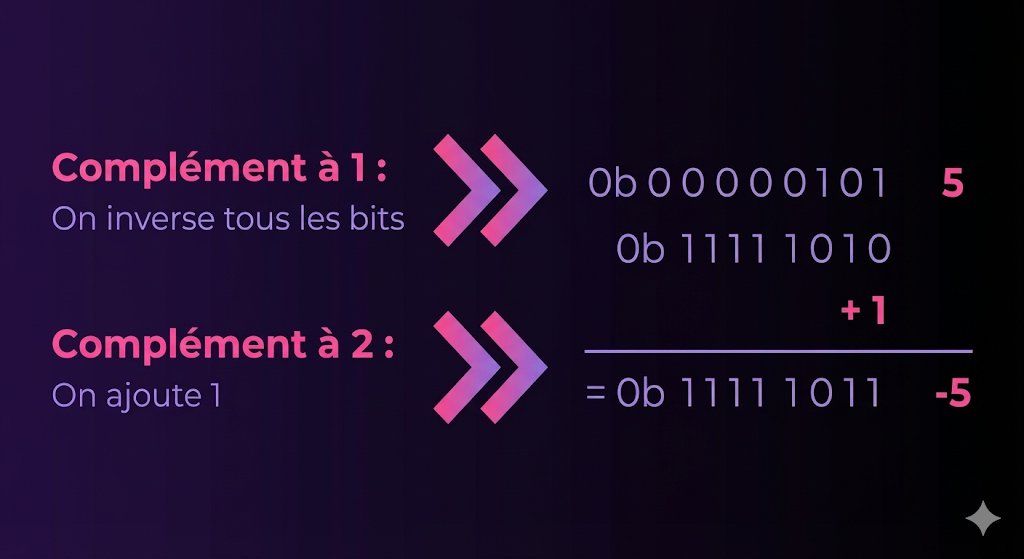

Trouver le nombre négatif — Complément à 2

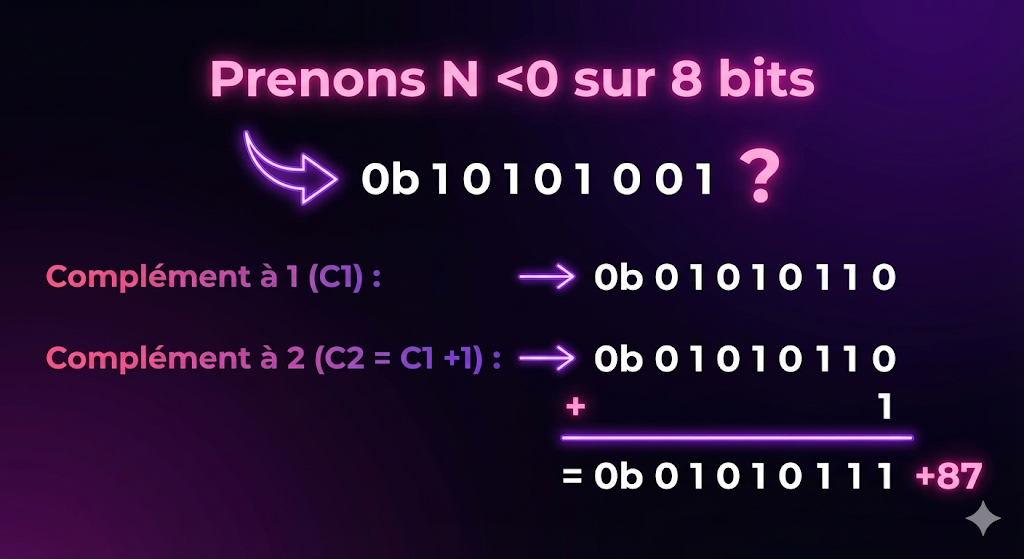

Un nombre négatif dont le MSB est 1 peut être identifié en trouvant son complément à 2 !

Méthode pour calculer le complément à 2 :

- Inverser tous les bits (complément à 1)

- Ajouter 1 au résultat

Dans l'exemple du schéma, N vaut −87.

Soustraction (base 2)

Voici le principe de la soustraction pour deux entiers :

La soustraction est réalisée en additionnant A avec le complément à 2 de B. Cela permet à l'ALU du processeur de ne disposer que d'un seul circuit d'addition.

Multiplication par une puissance de 2

La multiplication d'un entier a codé sur n bits par 2k (k > 0) est obtenue par un décalage de la suite de bits de k positions vers la gauche.

Les k bits de plus faible poids sont remplacés par des 0.

Si le résultat n'est pas représentable sur n bits, un débordement est généré.

Exemple : 0011 (= 3) × 22 = 1100 (= 12)

Division par une puissance de 2

La division d'un entier a codé sur n bits par 2k (k > 0) est obtenue par un décalage de la suite de bits de k positions vers la droite.

Il existe deux types de décalage :

- Décalage arithmétique (ASR — Arithmetic Shift Right) : le bit de signe Sn−1 est recopié dans les k bits de poids fort. Préserve le signe du nombre.

- Décalage logique (LSR — Logical Shift Right) : les k positions de poids fort sont remplies de 0. Le signe peut changer.

Exemple avec 1011 0000 (nombre négatif sur 8 bits), décalage de 2 positions (k = 2) :

- ASR :

_ _ 10 1100→ remplit avec des 1 →1110 1100(reste négatif) - LSR :

_ _ 10 1100→ remplit avec des 0 →0010 1100(devient positif — invalide pour les entiers signés)